# INVESTOR MEETING 2014

## William Holt

Executive Vice President General Manager, Technology and Manufacturing Group

# Key Messages from 2013

Intel Continues to Deliver the Benefits of Moore's Law

True Cost Reduction Remains Possible in a Capital Intensive Environment 📢

The Benefits of Technology Apply Across the Product Portfolio

# 14nm Status - 2013

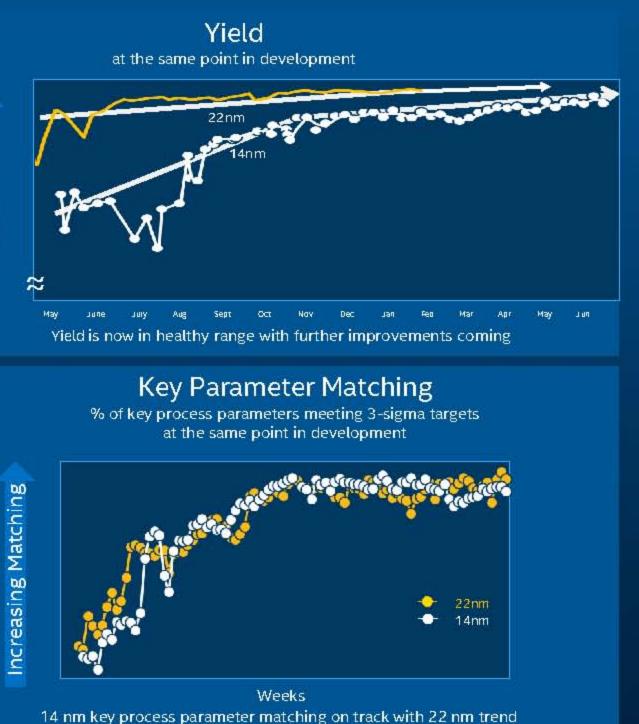

Yield at the same point in development 22nm 2 May June July Sept OCT Yield rapidly increasing, on track for matched yield in Q1 '14 \*

### **Key Parameter Matching**

% of key process parameters meeting 3-sigma targets at the same point in development

Increasing Matching

Increasing Yield

14 nm key process parameter matching on track with 22 nm trend

Performance Improvement

Switching Energy vs. Gate Delay

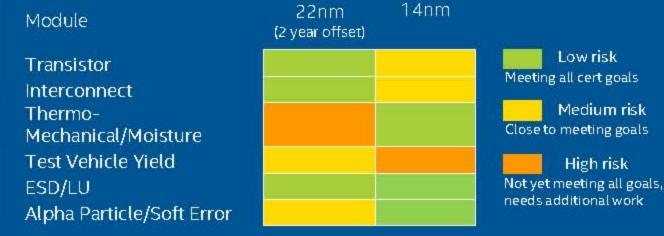

**Reliability Scorecard** at the same point in development

Generally healthy reliability at this stage, on track for Q1 '14 certification \*

Source: Intel. \* Forecast

# 14nm Status - 2014

Increasing Yield

Performance Improvement

Switching Energy vs. Gate Delay

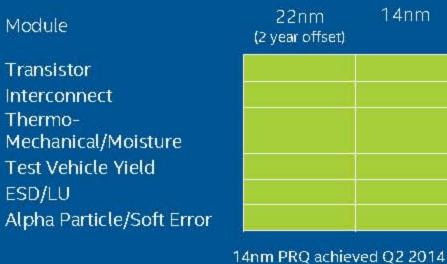

**Reliability Scorecard** at the same point in development

Source: Intel

14nm

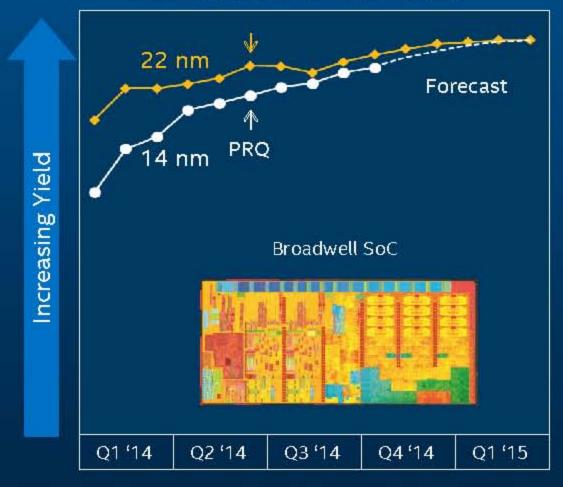

# 14 nm Product Yield Is In Healthy Range

14nm Broadwell Yield Trend

22 nm data are shifted to align date of lead product qual Depicts relative health, lines not to scale

## 22nm Is Intel's Highest Yielding Process Ever

Source: Intel

# 14nm Technology Overview

A True 14 nm Technology

2nd Generation FinFET

52 nm Interconnect Pitch

First Use of Air Gaps

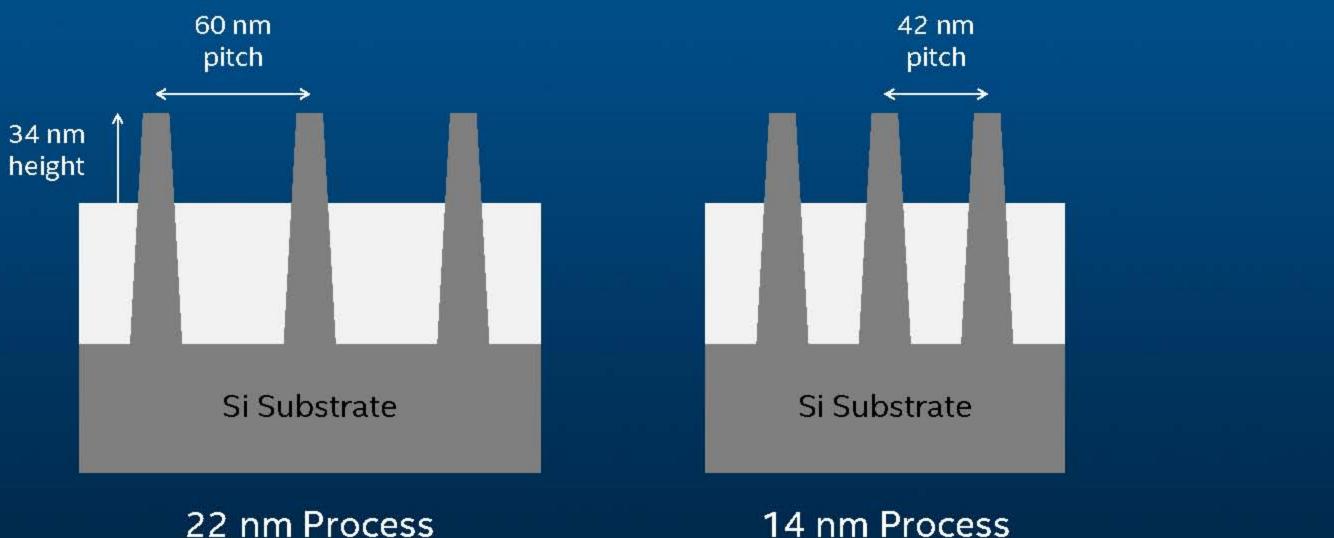

# Intel Has Developed a True 14 nm Technology

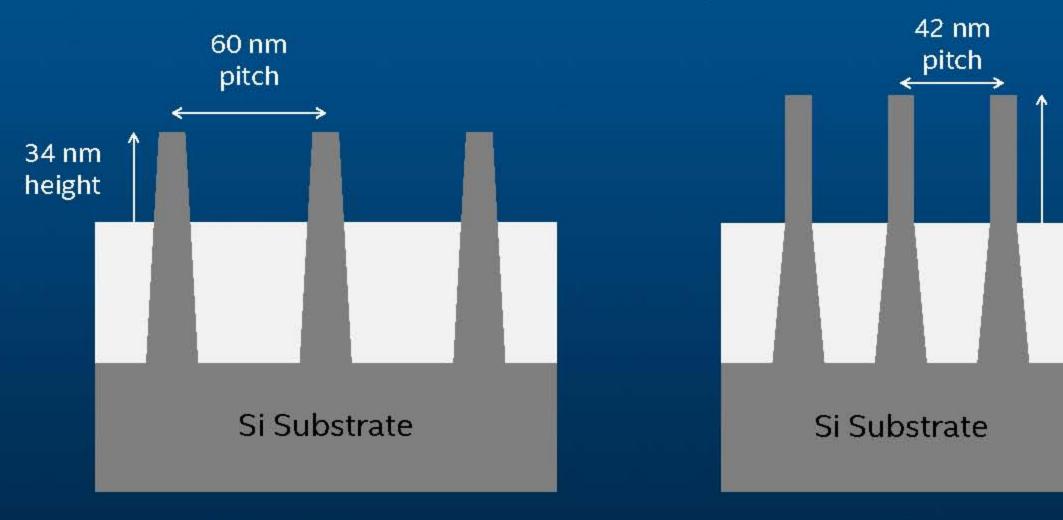

|                       | 22 nm<br>Node | 14 nm<br>Node | Sc |

|-----------------------|---------------|---------------|----|

| Transistor Fin Pitch  | 60            | 42            | .7 |

| Transistor Gate Pitch | 90            | 70            | .7 |

| Interconnect Pitch    | 80            | 52            | .6 |

|                       | nm            | nm            |    |

- cale 70x

- 78x

- 55x

# SRAM Memory Cells

### 22 nm Process

### 14 nm Process

## .108 um<sup>2</sup> (Used on CPU products)

.0588 um<sup>2</sup> (0.54x area scaling)

14 nm Design Rules + 2<sup>nd</sup> Generation Tri-gate Transistor Provides Industry-leading SRAM Density

22 nm Process

14 nm Process

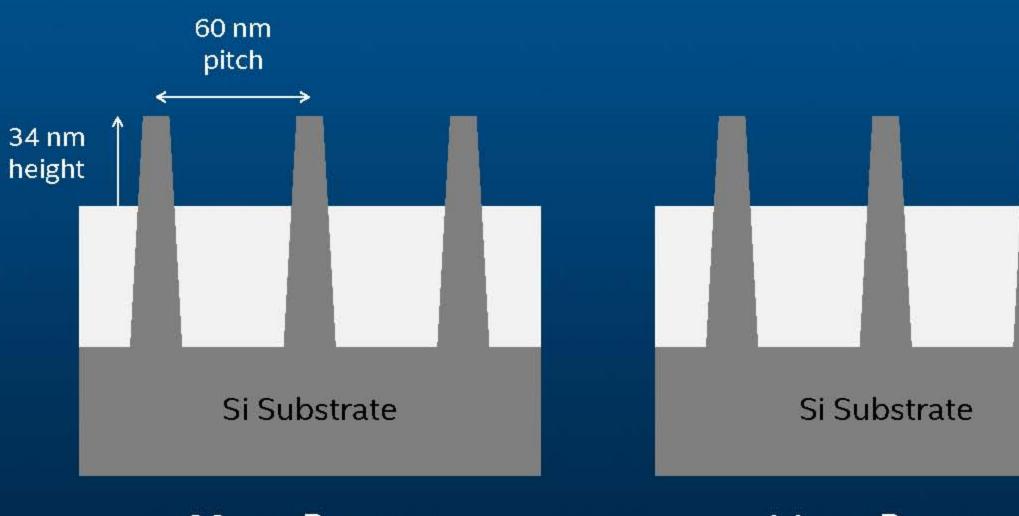

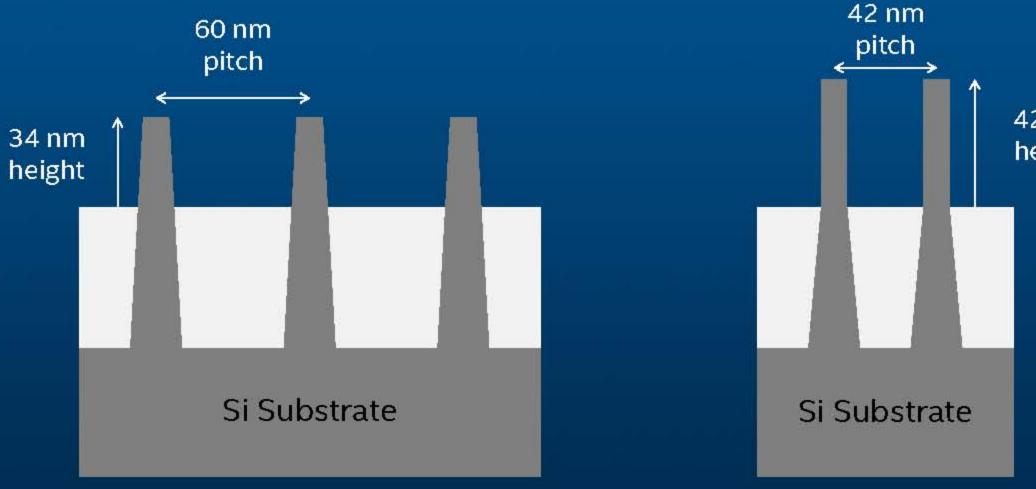

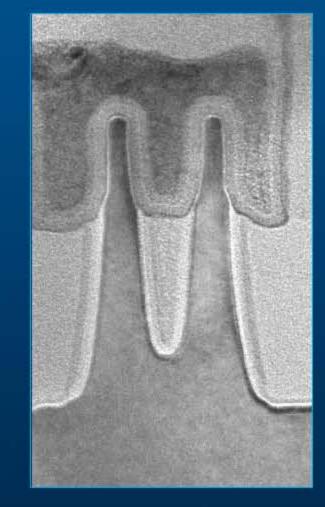

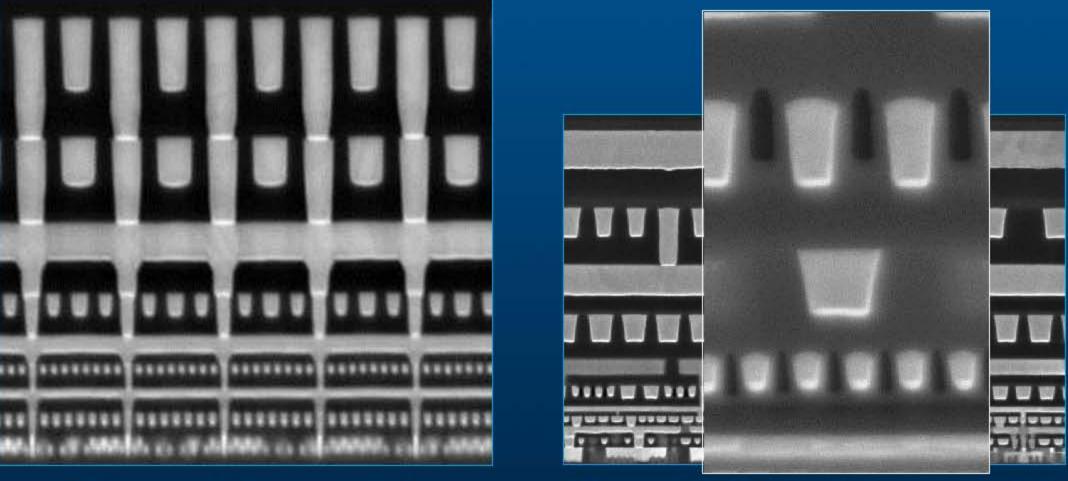

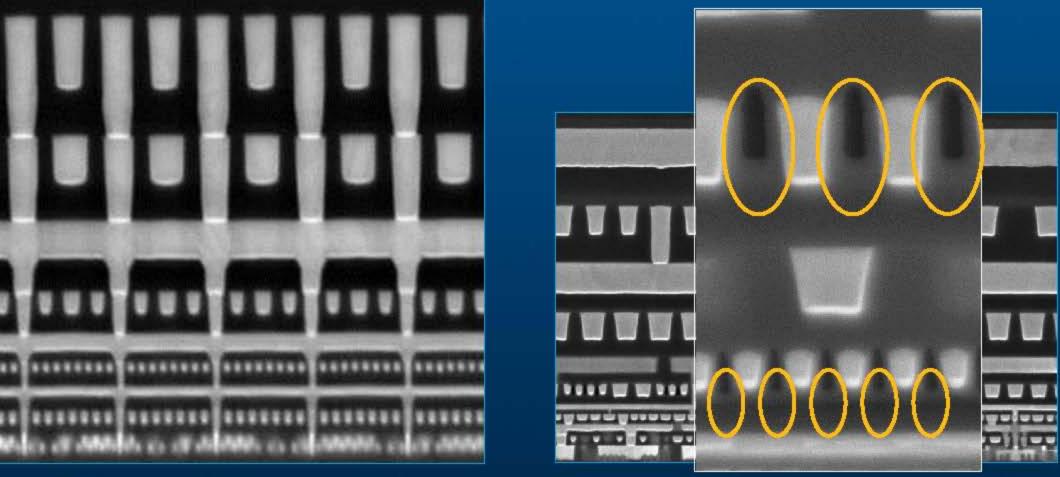

**Tighter Fin Pitch for Improved Density**

22 nm Process

14 nm Process

Taller and Thinner Fins for Increased Drive Current and Performance

### 42 nm height

22 nm Process

14 nm Process

Reduced Number of Fins for Improved Density and Lower Capacitance

### 42 nm height

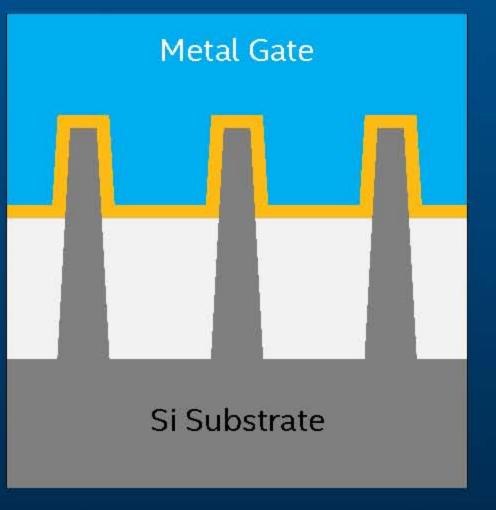

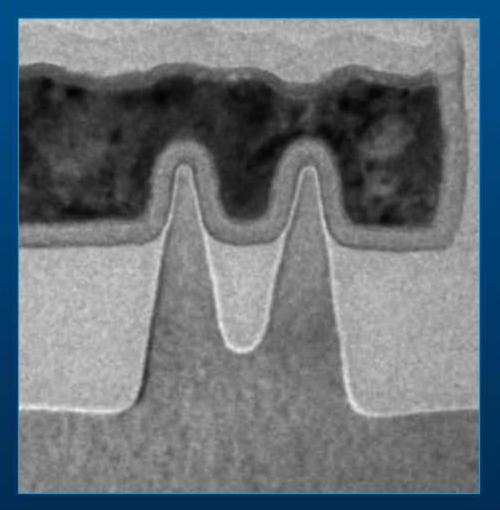

22 nm 1<sup>st</sup> Generation **Tri-gate Transistor**

14 nm 2<sup>nd</sup> Generation **Tri-gate Transistor**

22 nm 1<sup>st</sup> Generation Tri-gate Transistor 14 nm 2<sup>nd</sup> Generation Tri-gate Transistor

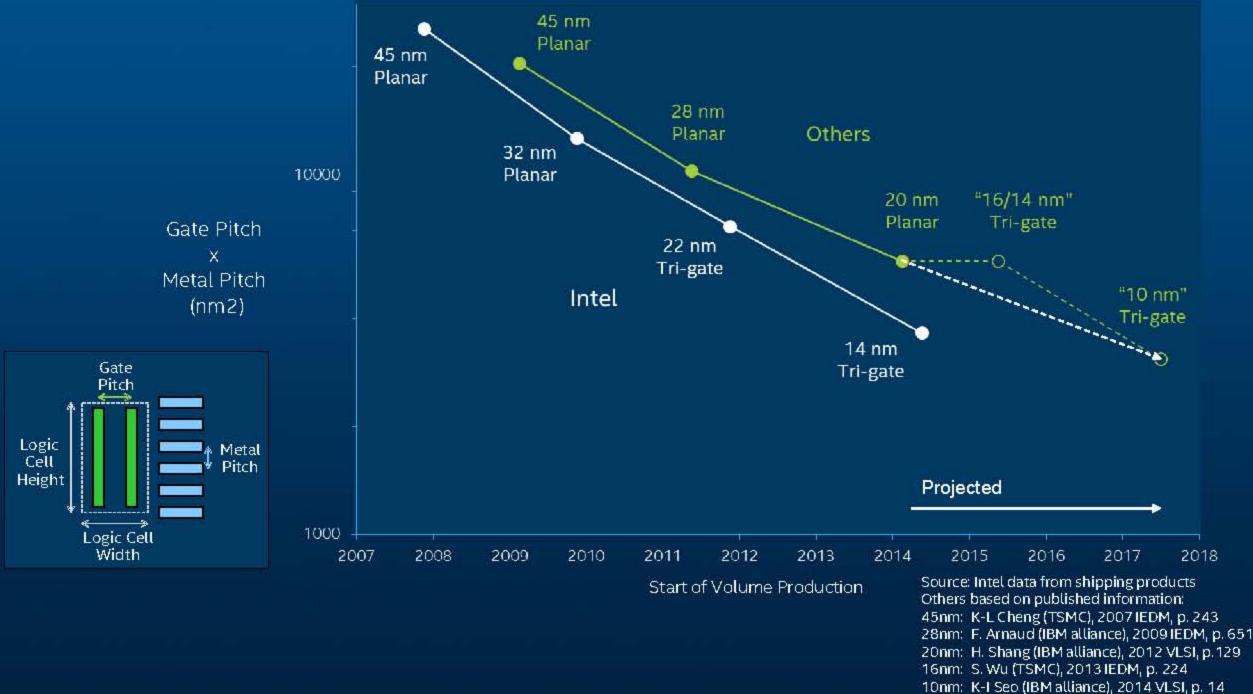

# Intel Transistor Leadership

Projected

\*Other names and brands may be claimed as the property of others. Source: Dates are based on start of high volume production. Projected dates are based on other company public statements.

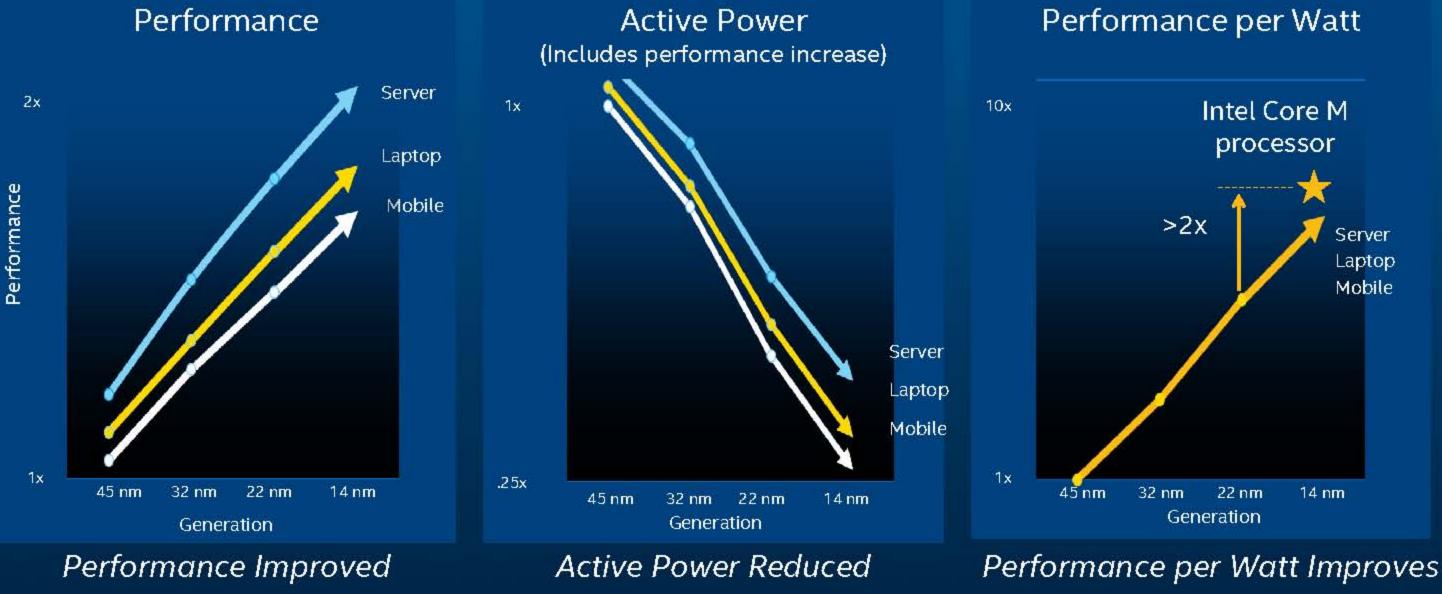

## 2<sup>nd</sup> Generation Tri-Gate is the Critical Enabler

14 nm BDW-Y Delivers >2x Improvement in Performance per Watt

Source: Intel

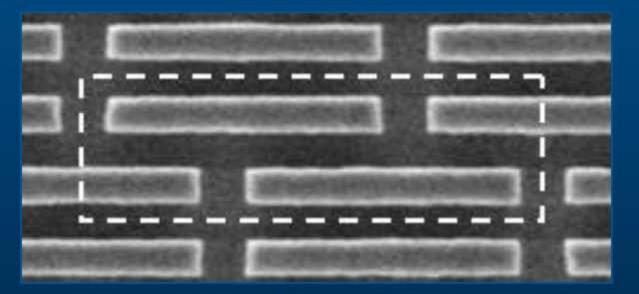

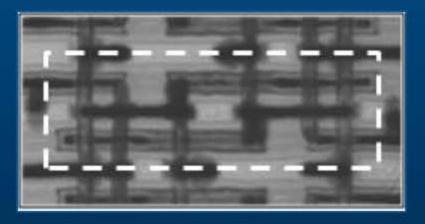

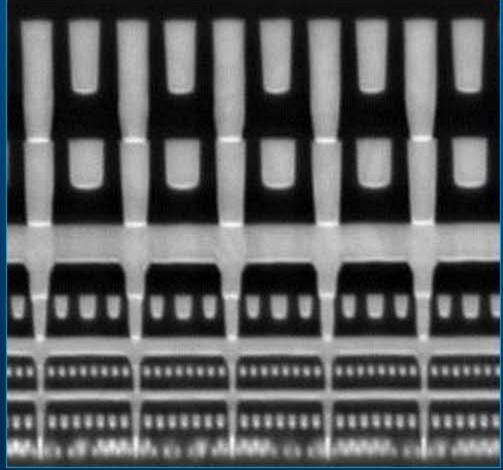

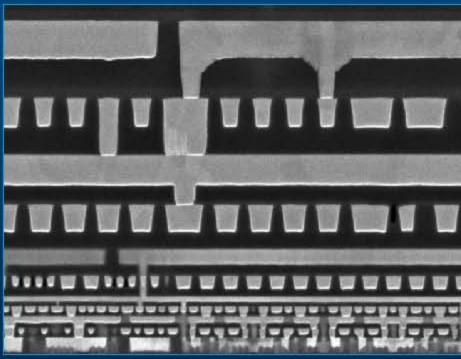

### Interconnects 22 nm Process 14 nm Process

### 80 nm minimum pitch

52 nm (0.65x) minimum pitch

52 nm Interconnect Pitch Provides Better-than-normal Interconnect Scaling

Source: Intel

### Interconnects 22 nm Process 14 nm Process

### 80 nm minimum pitch

52 nm (0.65x) minimum pitch

52 nm Interconnect Pitch Provides Better-than-normal Interconnect Scaling

### Interconnects 22 nm Process 14 nm Process

80 nm minimum pitch

52 nm (0.65x) minimum pitch

52 nm Interconnect Pitch Provides Better-than-normal Interconnect Scaling First Use of Air Gaps to Improve Interconnect Performance

Source: Intel

# Logic Area Scaling Trend

(Publicly available scaling information)

2018

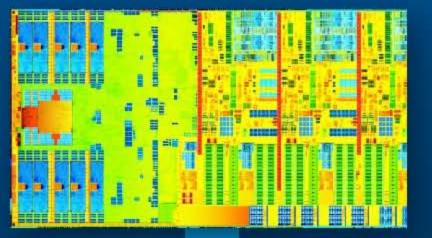

# 14nm Enables Cost and Performance Benefits

## Haswell 2 X 2 (22nm)

960M Transistors

## Broadwell delivers:

- 2.2x increase in transistor density 0

- Up to 40% better 3D graphics perf<sup>1</sup> 0

35% More Transistors

37% Smaller

Enables <9mm fanless designs •

## Broadwell 2 X 2 (14nm)

**1.3B transistors**

## Industry's First 14 nm Processor in Volume Production

Intel® Core™ M-5Y70 processor compared to Intel® Core™ i5-4302Y processor

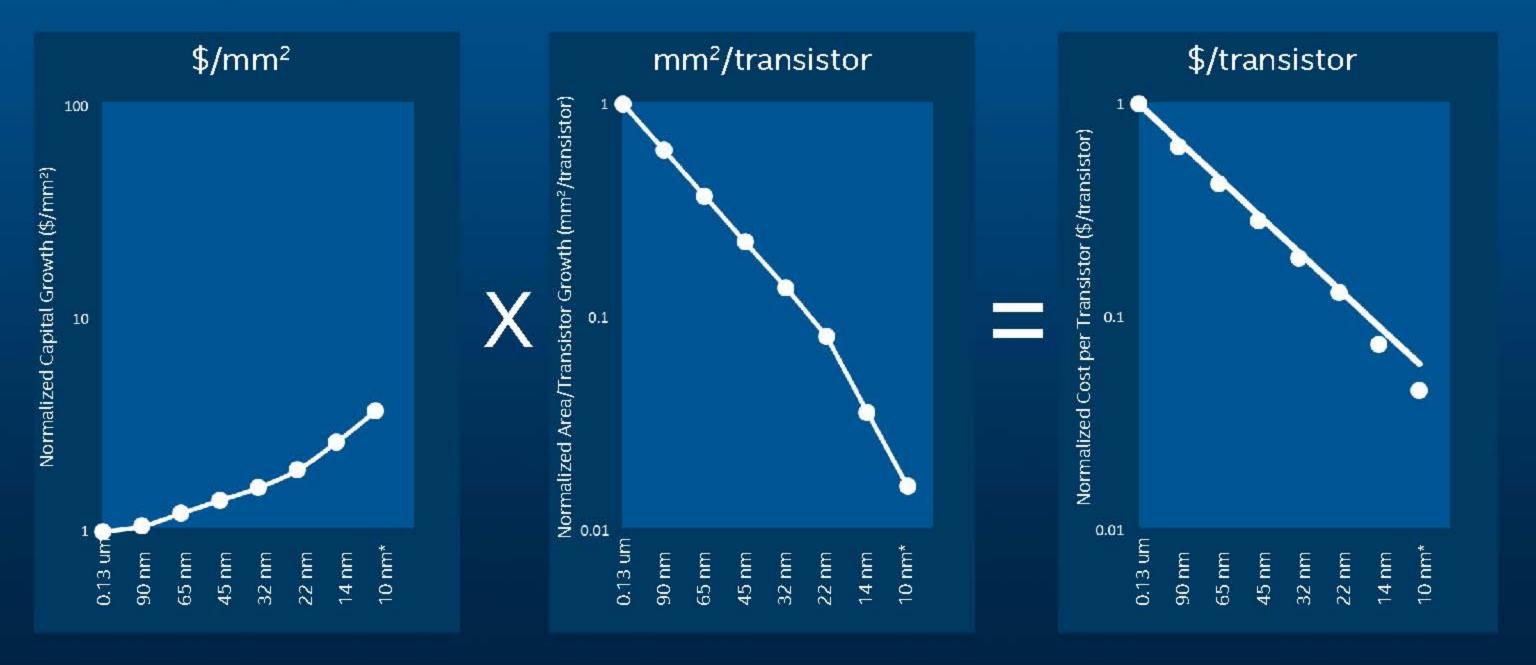

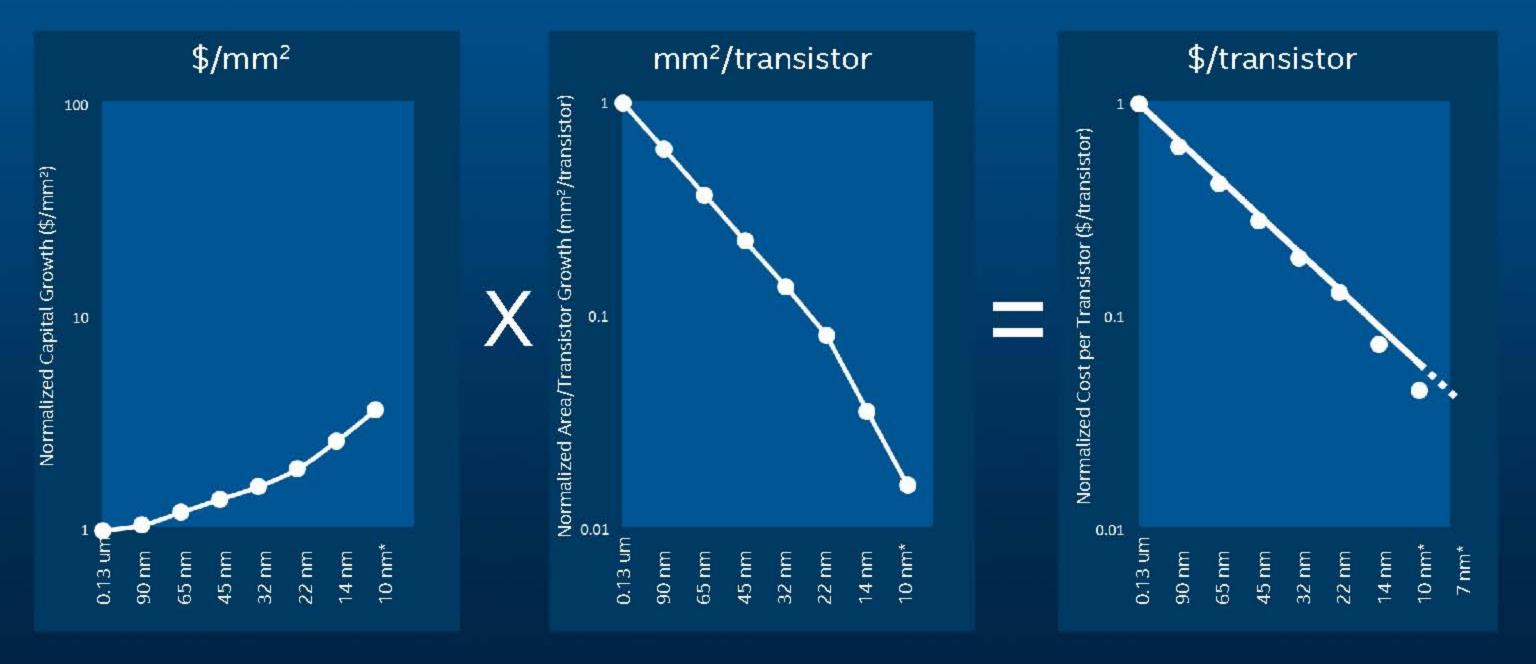

# Cost Reduction On Track

\* Forecast

# Cost Reduction On Track

\* Forecast

## Intel Continues to Deliver Moore's Law

## **True Cost Reduction Remains Possible**

## **Technology Enables Real Product Improvements**

# Legal Disclaimers

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products.

Intel technologies may require enabled hardware, specific software, or services activation. Check with your system manufacturer or retailer.

Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit <u>http://www.intel.com/benchmarks</u>

All dates, forecasts and products specified in this presentation are subject to change without notice. This presentation will not be updated to reflect any such changes.

Copyright 2014 Intel Corporation.

\*Other names and brands may be claimed as the property of others.

# **Risk Factors**

The statements in the presentations and other commentary that refer to plans and expectations for the fourth guarter, the year and the future are forward-looking statements that involve a number of risks and uncertainties. Words such as "anticipates," "expects," "intends," "plans," "believes," "seeks," "estimates," "may," "will," "should" and their variations identify forward-looking statements. Statements that refer to or are based on projections, uncertain events or assumptions also identify forward-looking statements. Many factors could affect Intel's actual results, and variances from Intel's current expectations regarding such factors could cause actual results to differ materially from those expressed in these forward-looking statements. Intel presently considers the following to be important factors that could cause actual results to differ materially from the company's expectations.

- Demand for Intel's products is highly variable and could differ from Intel's expectations due to factors including changes in the business and economic conditions; consumer confidence or income levels; customer acceptance of Intel's and competitors' products; competitive and pricing pressures, including actions taken by competitors; supply constraints and other disruptions affecting customers; changes in customer order patterns including order cancellations; and changes in the level of inventory at customers.

- Intel's gross margin percentage could vary significantly from expectations based on capacity utilization; variations in inventory valuation, including variations related to the timing of qualifying products for sale; changes in revenue levels; segment product mix; the timing and execution of the manufacturing ramp and associated costs; excess or obsolete inventory; changes in unit costs; defects or disruptions in the supply of materials or resources; and product manufacturing quality/yields. Variations in gross margin may also be caused by the timing of Intel product introductions and related expenses, including marketing expenses, and Intel's ability to respond quickly to technological developments and to introduce new features into existing products, which may result in restructuring and asset impairment charges.

- Intel operates in highly competitive industries and its operations have high costs that are either fixed or difficult to reduce in the short term.

- The declaration and rate of dividend payments and the amount and timing of Intel's stock buyback program are at the discretion of Intel's board of directors, and plans for future dividends and stock buy backs and could be affected by changes in Intel's priorities for the use of cash, such as operational spending, capital spending, acquisitions, and because of changes to Intel's cash flows and changes in tax laws.

- Intel's expected tax rate is based on current tax law and current expected income and may be affected by the jurisdictions in which profits are determined to be earned and taxed; changes in the estimates of credits, benefits and deductions; the resolution of issues arising from tax audits with various authorities, including payment of interest and penalties; and the ability to realize deferred tax assets.

- Gains or losses from equity securities and interest and other could vary from expectations depending on gains or losses on the sale, exchange, change in the fair value or impairments of debt and equity investments; interest rates; cash balances; and changes in fair value of derivative instruments.

- Intel's results could be affected by adverse economic, social, political and physical/infrastructure conditions in countries where Intel, its customers or its suppliers operate, including military conflict and other security risks, natural disasters, infrastructure disruptions, health concerns and fluctuations in currency exchange rates.

- Intel's results could be affected by the timing of closing of acquisitions, divestitures and other significant transactions.

- Intel's results could be affected by adverse effects associated with product defects and errata (deviations from published specifications), and by litigation or regulatory matters involving intellectual property, stockholder, consumer, antitrust, disclosure and other issues. An unfavorable ruling could include monetary damages or an injunction prohibiting Intel from manufacturing or selling one or more products, precluding particular business practices, impacting Intel's ability to design its products, or requiring other remedies such as compulsory licensing of intellectual property.

A detailed discussion of these and other factors that could affect Intel's results is included in Intel's SEC filings, including the company's most recent Form 10-Q, Form 10-K and earnings release.

# Configuration Information

- Intel<sup>®</sup> Core<sup>™</sup> M-5Y70 Processor (up to 2.60GHz, 4T/2C, 4M Cache) On Intel Reference Platform. BIOS: v80.1 Graphics: Intel® HD Graphics (driver v. 15.36.3650) Memory: 4 GB (2x2GB) Dual Channel LPDDR3-1600 SDD: Intel® 160GB OS: Windows\* 8.1 Update RTM

- Prior generation: Intel<sup>®</sup> Core<sup>™</sup> i5-4302Y (up to 2.30GHz, 4T/2C, 3M Cache) on Intel Reference Platform. 4.5W Thermal Design Power. BIOS:WTM 137 Graphics : Intel® HD Graphics (driver v. 15.36.3650) Memory: 4 GB (2x2GB) Dual Channel LPDDR3-1600 SDD: Intel® 160GB OS: Windows\* 8.1 Update RTM. System Power Management Policy: Balance Wireless: On and connected. Battery size assumption: 35WHr.

## INVESTOR MEETING 2014 SANTA CLARA NOVEMBER 20